- 您现在的位置:买卖IC网 > Sheet目录479 > MRF49XAT-I/ST (Microchip Technology)IC RF TXRX 433/868/915 16-TSSOP

�� �

�

�

�MRF49XA�

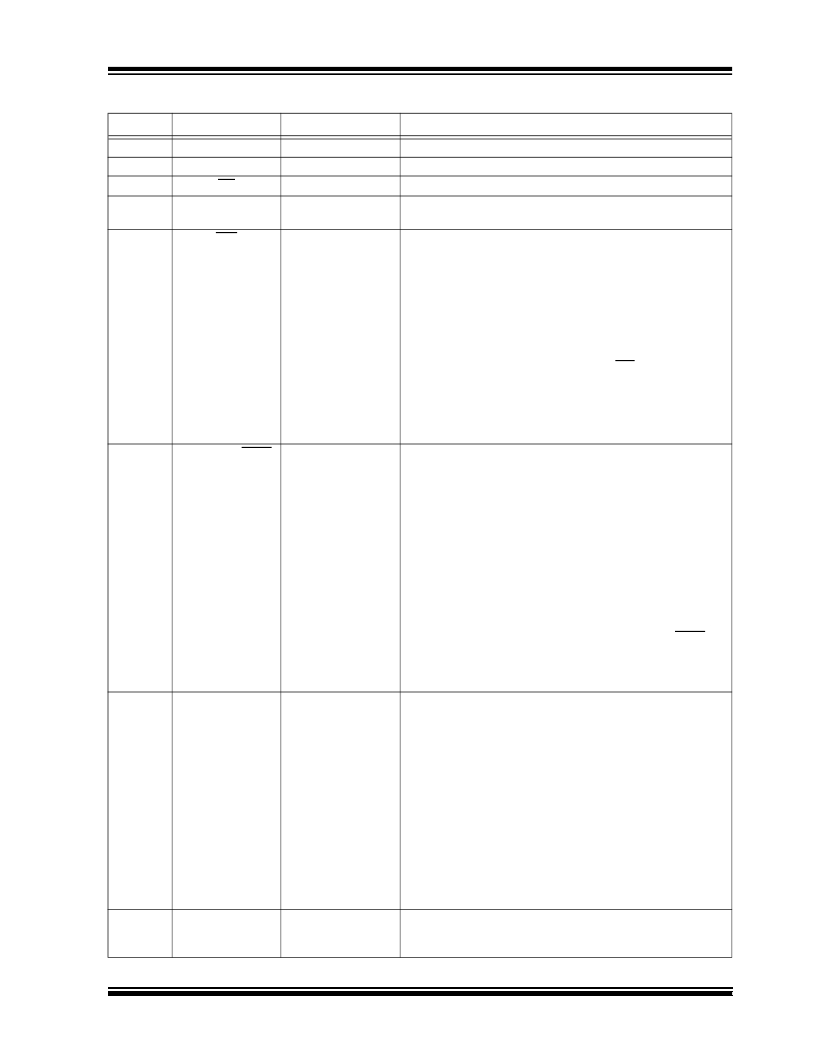

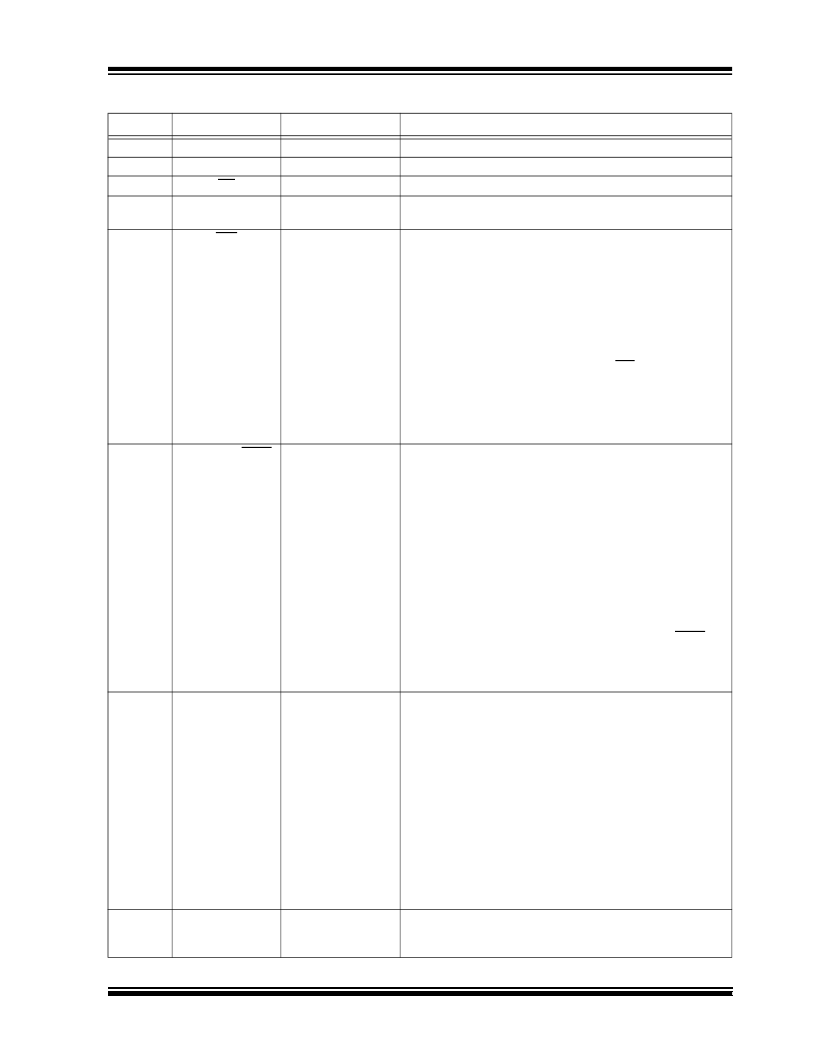

�TABLE� 2-1:�

�PIN� DESCRIPTION�

�Pin�

�1�

�2�

�3�

�4�

�Symbol�

�SDI�

�SCK�

�CS�

�SDO�

�Type�

�Digital� Input�

�Digital� Input�

�Digital� Input�

�Digital� Output�

�Description�

�Serial� data� input� interface� to� MRF49XA� (SPI� input� signal).�

�Serial� clock� interface� (SPI� clock).�

�Serial� interface� chip� select� (SPI� chip/device� select).�

�Serial� data� output� interface� from� MRF49XA� (SPI� output�

�signal).�

�5�

�IRO�

�Digital� Output�

�Interrupt� Request� Output:� Receiver� generates� an�

�active-low� interrupt� request� for� the� microcontroller� on� the�

�following� events:�

�?� The� TXBREG� (see� Table� 2-4� )� is� ready� to� receive� the�

�next� byte.�

�?� The� RXFIFOREG� (see� Table� 2-4� )� has� received� the�

�preprogrammed� amount� of� bits.�

�?� RXFIFOREG� overflow/TXBREG� underrun.�

�?� Negative� pulse� on� interrupt� input� pin� (INT).�

�?� Wake-up� timer� time-out.�

�?� Supply� voltage� below� the� preprogrammed� value� is�

�detected.�

�?� Power-on� Reset� (POR).�

�6�

�FSK/DATA/FSEL�

�Digital� Input/Output�

�Frequency� Shift� Keying:� Transmit� FSK� data� input� (with�

�internal� pull-up� resistor� of� 133� k� Ω� ).�

�Data:� When� configured� as� DATA,� this� pin� functions� as�

�follows:�

�?� Data� In:� Manually� modulates� the� data� from� the� external�

�host� microcontroller� when� the� internal� TXBREG� is� dis-�

�abled.� If� the� TXBREG� is� enabled,� this� pin� can� be� tied�

�“high”� or� left� unconnected.� When� reading� the� internal�

�RXFIFOREG,� this� pin� must� be� pulled� “low”.�

�?� Data� Out:� Receives� data� in� conjunction� with� RCLKOUT�

�when� the� internal� FIFO� is� not� used.�

�FIFO� Select:� Selects� the� FIFO� and� the� first� bit� appears� on�

�the� next� clock� when� reading� the� RXFIFOREG.� The� FSEL� pin�

�has� an� internal� pull-up� resistor.� This� pin� must� be� “high”� when�

�the� TX� register� is� enabled.� In� order� to� achieve� minimum�

�current� consumption,� keep� this� pin� “high”� in� Sleep� mode.�

�7�

�RCLKOUT/FCAP/�

�FINT�

�Digital� Input/Output�

�Recovery� Clock� Output:� Provides� the� clock� recovered� from�

�the� incoming� data� if:�

�?� FTYPE� bit� of� BBFCREG� (see� Table� 2-10� )� is� configured�

�as� digital� filter� and�

�?� FIFO� is� disabled� by� configuring� FIFOEN� bit� of�

�GENCREG� (see� Table� 2-10� )�

�Filter� Capacitor:� This� pin� is� a� raw� baseband� data� if� the�

�FTYPE� bit� of� BBFCREG� is� configured� as� a� configuration�

�filter.� The� pin� can� be� used� by� the� host� microcontroller� for� data�

�recovery.�

�FIFO� Interrupt:� When� the� internal� FIFO,� FIFOEN� bit� of�

�GENCREG� is� enabled,� this� pin� acts� as� a� FIFO� full� interrupt,�

�indicating� that� the� FIFO� has� been� filled� to� its� preprogrammed�

�limit� (see� FFBC<3:0>� bits� in� FIFORSTREG� in� Table� 2-10� ).�

�8�

�CLKOUT�

�Digital� Output�

�Clock� Output:� The� transceiver� ’s� clock� output� can� be� used� by�

�the� host� microcontroller� as� a� clock� source.� Refer� Register� 2�

�for� more� details.�

�?� 2009-2011� Microchip� Technology� Inc.�

�Preliminary�

�DS70590C-page� 11�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MRF89XA-I/MQ

TXRX ISM SUB-GHZ ULP 32QFN

MRF89XAM9A-I/RM

IC TXRX MOD 915MHZ ULP SUB-GHZ

MRX-001-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002SL-433DR-B

MODULE RCVR 433MHZ SAW LN 24DIP

MRX-005-915DR-B

MODULE RECEIVER 915MHZ 18DIP

MRX-005SL-915DR-B

MODULE RCVR 915MHZ SAW LN 24DIP

MRX-007-433DR-B

MODULE RECEIVER 433MHZ 18DIP

相关代理商/技术参数

MRF49XAT-I/T

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF49XAT-I-ST

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF49XAT-I-T

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF4A(AMMO)

制造商:Bel Fuse 功能描述:FUSE

MRF5

制造商:Ferraz Shawmut 功能描述:

MRF50

制造商:Ferraz Shawmut 功能描述:

MRF500

制造商:Ferraz Shawmut 功能描述:

MRF5003

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:N-CHANNEL BROADBAND RF POWER FET